# TMC2660C DATASHEET

Universal, cost-effective stepper driver for two-phase bipolar motors with state-of-the-art features. Integrated MOSFETs for up to 4 A motor current per coil. With Step/Dir Interface and SPI.

#### FEATURES AND BENEFITS

Drive Capability up to 4A motor current

Voltage up to 30V DC

Highest Resolution up to 256 microsteps per full step

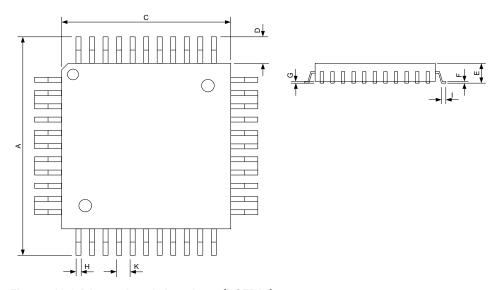

Compact Size 10x10mm QFP-44 package

$\textbf{Low Power Dissipation} \ \ \text{very low RDSON \& sync.} \ \ \text{rectification}$

EMI-optimized programmable slope

**Protection & Diagnostics** short to GND, overtemperature & undervoltage, overcurrent and short to VS (TMC2660C only)

StallGuard2™ high precision sensorless motor load detection

CoolStep™ load dependent current control saves up to 75%

MicroPlyer™ 256 microstep smoothness with 1/16 step input.

SpreadCycle™ high-precision chopper for best current sine wave form and zero crossing

Improved Silent Motor operation (TMC2660C only)

Stand Alone option (TMC2660C only)

#### **APPLICATIONS**

Textile, Sewing Machines

Factory Automation

Lab Automation

Liquid Handling

Medical

Office Automation

Printer and Scanner

CCTV, Security

ATM, Cash recycler

POS

Pumps and Valves

Heliostat Controller

CNC Machines

#### **DESCRIPTION**

The TMC2660 driver for two-phase stepper motors offers an industry-leading feature set, including high-resolution microstepping, sensorless mechanical load measurement, load-adaptive power optimization, and low-resonance chopper operation. Standard SPI™ and STEP/DIR interfaces simplify communication. Integrated power MOSFETs handle motor currents up to 2.2A RMS continuously or 2.8A RMS boost current per coil. Integrated protection and diagnostic features support robust and reliable operation. High integration, high energy efficiency and small form factor enable miniaturized designs with low external component count for cost-effective and highly competitive solutions.

The new -C device improves motor silence and adds low side short protection.

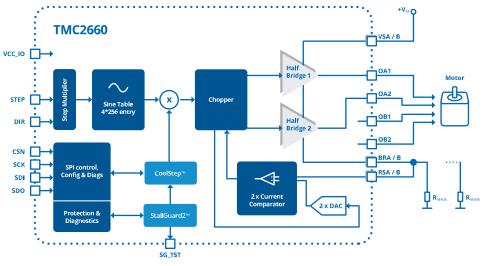

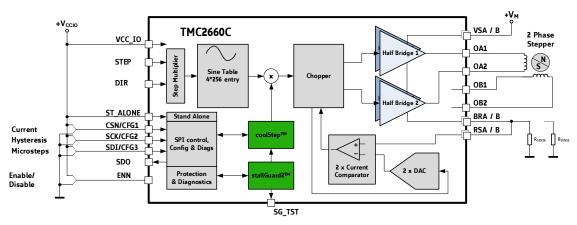

#### **BLOCK DIAGRAM**

#### APPLICATION EXAMPLES: SMALL SIZE – BEST PERFORMANCE

The TMC2660 scores with power density, integrated power MOSFETs, and a versatility that covers a wide spectrum of applications and motor sizes, all while keeping costs down. Extensive support at the chips, board, and software levels enables rapid design cycles and fast time-to-market with competitive products. High energy efficiency from TRINAMIC's CoolStep technology delivers further cost savings in related systems such as power supplies and cooling.

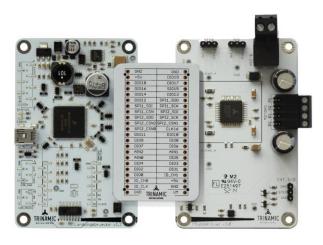

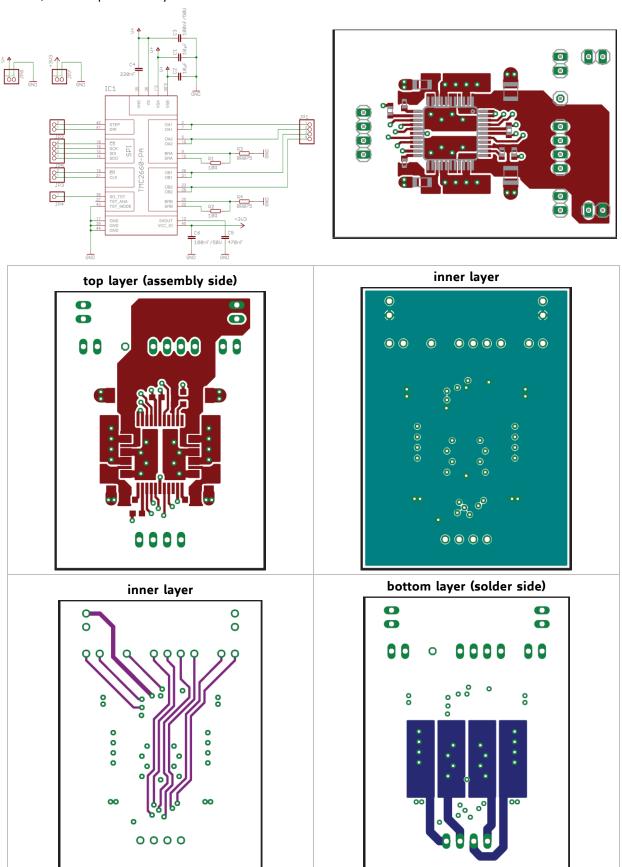

#### TMC4210+TMC2660-EVAL EVALUATION-BOARD FOR 1 AXIS

Evaluation board system with TMC2660

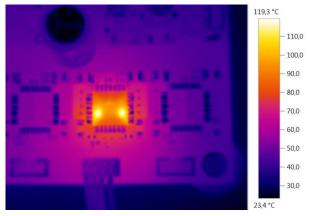

This evaluation board is a development platform for applications based on the TMC2660. The board features a USB interface for communication with the TMCL-IDE control software running on a PC. The power MOSFETs of the TMC2660 support drive currents up to 2.4A RMS and 29V.

The control software provides a user-friendly GUI for setting control parameters and visualizing the dynamic response of the motor.

Motor movement can be controlled through the Step/Dir interface using inputs from an external source or signals generated by the onboard microcontroller acting as a step generator. Optionally add a motion controller card between CPU board and TMC2660-EVAL.

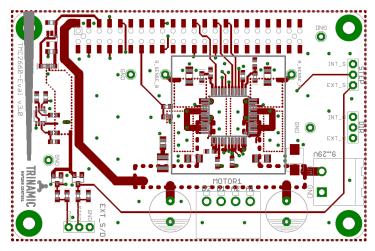

Top level layout of TMC2660-EVAL

#### **ORDER CODES**

| Order code     | PN        | Description                                           | Size [mm²] |

|----------------|-----------|-------------------------------------------------------|------------|

| TMC2660C-PA    | 00-0185   | CoolStep™ driver with internal MOSFETs, up to 30V DC, | 10 x 10    |

|                |           | QFP-44 with 12x12 pins                                |            |

| TMC2660-PA-T   | 00-0185-T | -T devices are packaged in tape on reel               |            |

| TMC2660-EVAL   | 40-0068   | Evaluation board for TMC2660.                         | 85 x 55    |

| LANDUNGSBRÜCKE | 40-0167   | Baseboard for TMC2660-EVAL and further evaluation     | 85 x 55    |

|                |           | boards                                                |            |

| ESELSBRÜCKE    | 40-0098   | Connector board for plug-in evaluation board system   | 61 x 38    |

<sup>\*)</sup> The term TMC2660 is used for TMC2660 or TMC2660C within this datasheet. Differences in the TMC2660C are explicitly marked with TMC2660C. See summary in section 15. Non-C-type information is only given for reference.

# TABLE OF CONTENTS

| 1  | PRI                      | NCIPLES OF OPERATION                                                                                                                     | 4          |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    | 1.1<br>1.2<br>1.3<br>1.4 | KEY CONCEPTS  CONTROL INTERFACES  MECHANICAL LOAD SENSING  CURRENT CONTROL                                                               | 5<br>5     |

| 2  |                          | ASSIGNMENTS                                                                                                                              |            |

|    | 2.1<br>2.2               | PACKAGE OUTLINESIGNAL DESCRIPTIONS                                                                                                       |            |

| 3  | INTI                     | ERNAL ARCHITECTURE                                                                                                                       | 8          |

| 4  | STA                      | NDALONE OPERATION                                                                                                                        | 9          |

| 5  | STA                      | LLGUARD2 LOAD MEASUREMENT                                                                                                                | .10        |

|    | 5.1<br>5.2<br>5.3<br>5.4 | TUNING THE STALLGUARD2 THRESHOLD STALLGUARD2 MEASUREMENT FREQUENCY AND FILTERING DETECTING A MOTOR STALL LIMITS OF STALLGUARD2 OPERATION | .12<br>.12 |

| 6  |                          | LSTEP LOAD-ADAPTIVE CURRENT                                                                                                              | .13        |

|    | 6.1                      | TUNING COOLSTEP                                                                                                                          | .15        |

| 7  | SPI                      | INTERFACE                                                                                                                                | .16        |

|    | 7.1<br>7.2               | BUS SIGNALS                                                                                                                              |            |

|    | 7.3                      | BUS ARCHITECTURE                                                                                                                         |            |

|    | 7.4                      | REGISTER WRITE COMMANDS                                                                                                                  |            |

|    | 7.5<br>7.6               | DRIVER CONTROL REGISTER (DRVCTRL) CHOPPER CONTROL REGISTER (CHOPCONF                                                                     | -)         |

|    | 7.7                      | COOLSTEP CONTROL REGISTER (SMARTEN                                                                                                       | )          |

|    | 7.8                      | STALLGUARD2 CONTROL REGISTER (SGCSCONF)                                                                                                  |            |

|    | 7.9                      | DRIVER CONTROL REGISTER (DRVCONF)                                                                                                        |            |

|    | 7.10<br>7.11             | READ RESPONSE  DEVICE INITIALIZATION                                                                                                     |            |

| 8  |                          | P/DIR INTERFACE                                                                                                                          |            |

| Ĭ  | 8.1                      | TIMING                                                                                                                                   |            |

|    | 8.2                      | MICROSTEP TABLE                                                                                                                          |            |

|    | 8.3                      | CHANGING RESOLUTION                                                                                                                      |            |

|    | 8.4<br>8.5               | MICROPLYER STEP INTERPOLATORSTANDSTILL CURRENT REDUCTION                                                                                 |            |

| 9  | CUR                      | RENT SETTING                                                                                                                             |            |

|    | 9.1                      | Sense Resistors                                                                                                                          |            |

| 10 | сно                      | PPER OPERATION                                                                                                                           | .34        |

|    | 10.1                     | SPREADCYCLE CHOPPER                                                                                                                      |            |

|    | 10.2                     | CONSTANT OFF-TIME MODE                                                                                                                   |            |

| 1: | 1 POV                    | VER MOSFET STAGE                                                                                                                         | .40        |

|    | 11 1                     | BREAK-BEFORE-MAKE LOGIC                                                                                                                  | 40         |

| 11                   | 2                 | ENN INPUT                 | 40             |

|----------------------|-------------------|---------------------------|----------------|

| 12                   | DIA               | GNOSTICS AND PROTECTION4  | <b>1</b> 1     |

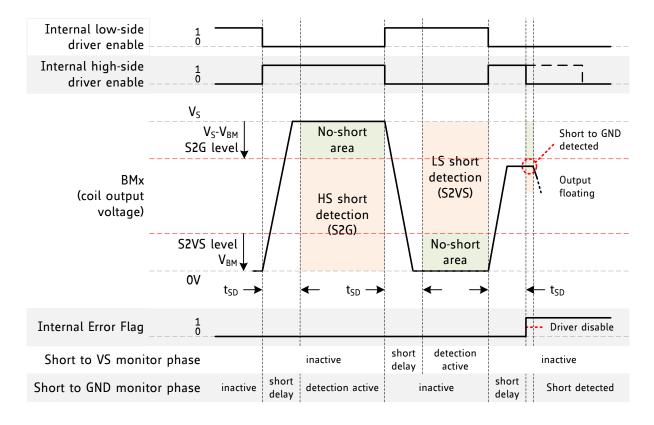

| 12<br>12<br>12<br>12 | 2.3               | SHORT PROTECTION          | 42<br>43       |

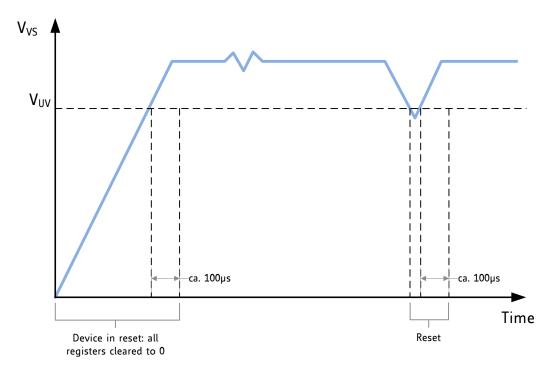

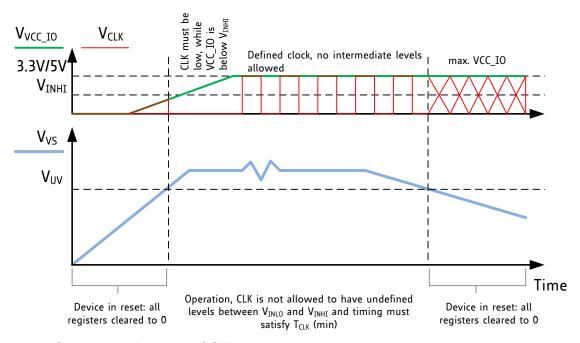

| 13                   | POW               | VER SUPPLY SEQUENCING4    | ¥5             |

| 14                   | SYS               | TEM CLOCK4                | ¥5             |

| 14                   | .1                | FREQUENCY SELECTION       | <del>1</del> 6 |

| 15                   | СОМ               | PATIBILITY TO NON-C-TYPE4 | ¥7             |

| 16                   | LAY               | OUT CONSIDERATIONS4       | 48             |

| 16<br>16<br>16<br>16 | 5.2<br>5.3<br>5.4 | SENSE RESISTORS           | 48<br>48<br>48 |

| 17                   | ABS               | OLUTE MAXIMUM RATINGS     | 50             |

| 18                   | ELEC              | TRICAL CHARACTERISTICS    | 51             |

| 18                   | 3.1<br>3.2<br>3.3 | OPERATIONAL RANGE         | 51             |

| 19                   | PAC               | KAGE MECHANICAL DATA      | 55             |

| 19<br>19             | ).1<br>).2        | DIMENSIONAL DRAWINGS      |                |

| 20                   | DISC              | CLAIMER                   | 56             |

| 21                   | ESD               | SENSITIVE DEVICE          | 56             |

| 22                   | DES               | IGNED FOR SUSTAINABILITY  | 56             |

| 23                   |                   | LE OF FIGURES             |                |

| 24                   | REV]              | ISION HISTORY             | 57             |

## 1 Principles of Operation

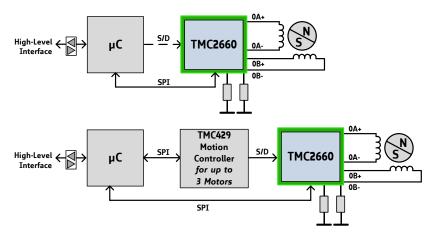

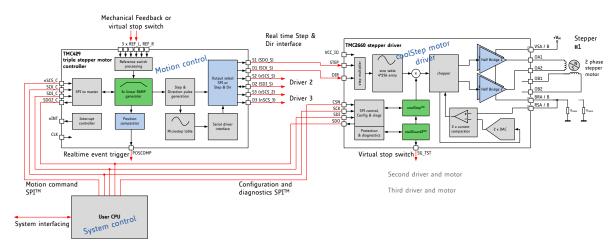

Figure 1.1 Block diagram: applications

The TMC2660 motor driver chip with included MOSFETs is the intelligence and power between a motion controller and the two phase stepper motor as shown in Figure 1.1. Following power-up, an embedded microcontroller initializes the driver by sending commands over an SPI bus to write control parameters and mode bits in the TMC2660. The microcontroller may implement the motion-control function as shown in the upper part of the figure, or it may send commands to a dedicated motion controller chip such as TRINAMIC's TMC429 as shown in the lower part.

The motion controller can control the motor position by sending pulses on the STEP signal while indicating the direction on the DIR signal. The TMC2660 has a microstep counter and sine table to convert these signals into the coil currents which control the position of the motor. If the microcontroller implements the motion-control function, it can write values for the coil currents directly to the TMC2660 over the SPI interface, in which case the STEP/DIR interface may be disabled. This mode of operation requires software to track the motor position and reference a sine table to calculate the coil currents.

To optimize power consumption and heat dissipation, software may also adjust CoolStep and StallGuard2 parameters in real-time, for example to implement different tradeoffs between speed and power consumption in different modes of operation.

The motion control function is a hard real-time task which may be a burden to implement reliably alongside other tasks on the embedded microcontroller. By offloading the motion-control function to the TMC429, up to three motors can be operated reliably with very little demand for service from the microcontroller. Software only needs to send target positions, and the TMC429 generates precisely timed step pulses. Software retains full control over both the TMC2660 and TMC429 through the SPI bus.

## 1.1 Key Concepts

The TMC2660 motor driver implements several advanced features which are exclusive to TRINAMIC products. These features contribute toward greater precision, greater energy efficiency, higher reliability, smoother motion, and cooler operation in many stepper motor applications.

StallGuard2™ High-precision load measurement using the back EMF on the coils

CoolStep™ Load-adaptive current control which reduces energy consumption by as much as

75%

SpreadCycle™ High-precision chopper algorithm available as an alternative to the traditional

constant off-time algorithm

MicroPlyer™ Microstep interpolator for obtaining increased smoothness of microstepping over a

STEP/DIR interface

In addition to these performance enhancements, TRINAMIC motor drivers also offer safeguards to detect and protect against shorted outputs, open-circuit output, overtemperature, and undervoltage conditions for enhancing safety and recovery from equipment malfunctions.

#### 1.2 Control Interfaces

There are two control interfaces from the motion controller to the motor driver: the SPI serial interface and the STEP/DIR interface. The SPI interface is used to write control information to the chip and read back status information. This interface must be used to initialize parameters and modes necessary to enable driving the motor. This interface may also be used for directly setting the currents flowing through the motor coils, as an alternative to stepping the motor using the STEP and DIR signals, so the motor can be controlled through the SPI interface alone.

The STEP/DIR interface is a traditional motor control interface available for adapting existing designs to use TRINAMIC motor drivers. Using only the SPI interface requires slightly more CPU overhead to look up the sine tables and send out new current values for the coils.

#### 1.2.1 SPI Interface

The SPI interface is a bit-serial interface synchronous to a bus clock. For every bit sent from the bus master to the bus slave, another bit is sent simultaneously from the slave to the master. Communication between an SPI master and the TMC2660 slave always consists of sending one 20-bit command word and receiving one 20-bit status word.

The SPI command rate typically corresponds to the microstep rate at low velocities. At high velocities, the rate may be limited by CPU bandwidth to 10-100 thousand commands per second, so the application may need to change to fullstep resolution.

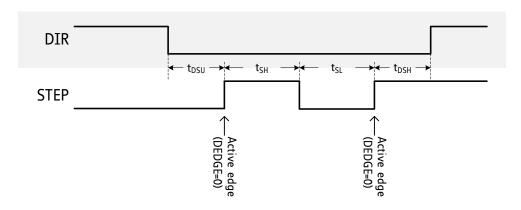

#### 1.2.2 STEP/DIR Interface

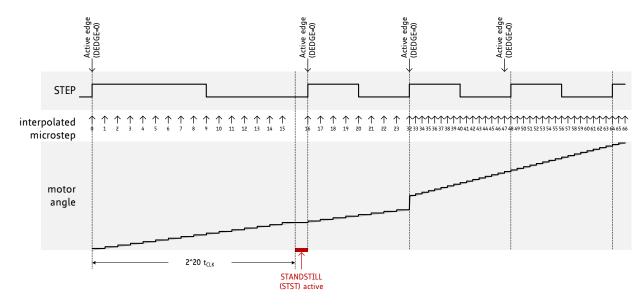

The STEP/DIR interface is enabled by default. Active edges on the STEP input can be rising edges or both rising and falling edges, as controlled by another mode bit (DEDGE). Using both edges cuts the toggle rate of the STEP signal in half, which is useful for communication over slow interfaces such as optically isolated interfaces.

On each active edge, the state sampled from the DIR input determines whether to step forward or back. Each step can be a fullstep or a microstep, in which there are 2, 4, 8, 16, 32, 64, 128, or 256 microsteps per fullstep. During microstepping, a step impulse with a low state on DIR increases the microstep counter and a high decreases the counter by an amount controlled by the microstep resolution. An internal table translates the counter value into the sine and cosine values which control the motor current for microstepping.

## 1.3 Mechanical Load Sensing

The TMC2660 provides StallGuard2 high-resolution load measurement for determining the mechanical load on the motor by measuring the back EMF. In addition to detecting when a motor stalls, this feature can be used for homing to a mechanical stop without a limit switch or proximity detector. The CoolStep power-saving mechanism uses StallGuard2 to reduce the motor current to the minimum motor current required to meet the actual load placed on the motor.

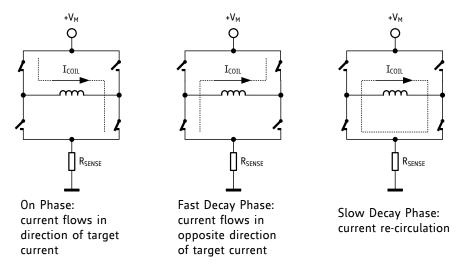

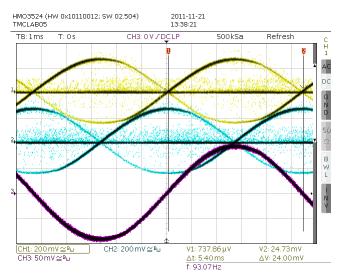

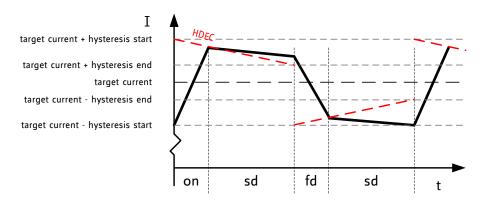

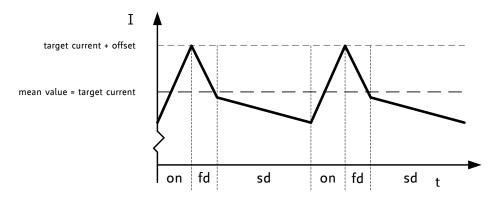

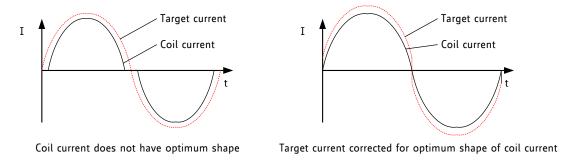

#### 1.4 Current Control

Current into the motor coils is controlled using a cycle-by-cycle chopper mode. Two chopper modes are available: a traditional constant off-time mode and the new SpreadCycle mode. SpreadCycle mode offers smoother operation and greater power efficiency over a wide range of speed and load.

# 2 Pin Assignments

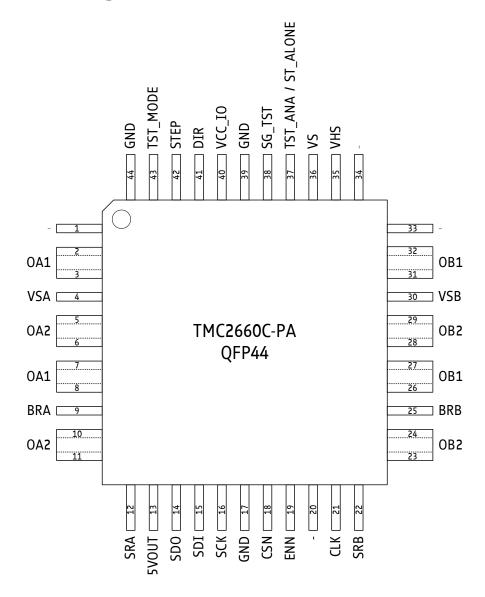

# 2.1 Package Outline

Figure 2.1 TMC2660 pin assignment (top view)

# 2.2 Signal Descriptions

| Pin | Number | Туре   | Function                                                             |

|-----|--------|--------|----------------------------------------------------------------------|

| OA1 | 2, 3   | 0 (VS) | Bridge A1 output. Interconnect all of these pins using thick traces  |

|     | 7, 8   |        | capable to carry the motor current and distribute heat into the PCB. |

| OA2 | 5, 6   | 0 (VS) | Bridge A2 output. Interconnect all of these pins using thick traces  |

|     | 10, 11 |        | capable to carry the motor current and distribute heat into the PCB. |

| OB1 | 26, 27 | 0 (VS) | Bridge B1 output. Interconnect all of these pins using thick traces  |

|     | 31, 32 |        | capable to carry the motor current and distribute heat into the PCB. |

| OB2 | 23, 24 | 0 (VS) | Bridge B2 output. Interconnect all of these pins using thick traces  |

|     | 28, 29 |        | capable to carry the motor current and distribute heat into the PCB. |

| VSA | 4      |        | Bridge A/B positive power supply. Connect to VS and provide          |

| VSB | 30     |        | sufficient filtering capacity for chopper current ripple.            |

| Pin                   | Number        | Туре                  | Function                                                                                                                                                                                                                                                                   |  |

|-----------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

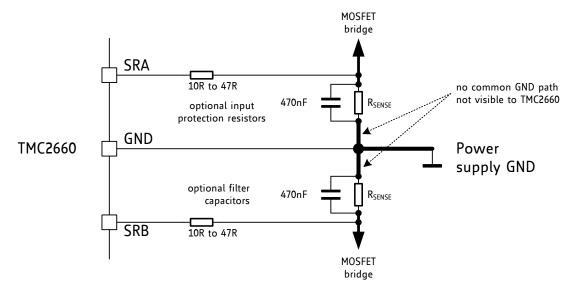

| BRA                   | 9             | ΑI                    | Bridge A/B negative power supply via sense resistor in bridge foot                                                                                                                                                                                                         |  |

| BRB                   | 25            |                       | point.                                                                                                                                                                                                                                                                     |  |

| SRA                   | 12            | ΑI                    | Sense resistor inputs for chopper current regulation.                                                                                                                                                                                                                      |  |

| SRB                   | 22            |                       |                                                                                                                                                                                                                                                                            |  |

| 5VOUT                 | 13            |                       | Output of the on-chip 5V linear regulator. This voltage is used to supply the low-side MOSFETs and internal analog circuitry. An external capacitor to GND close to the pin is required. Place the capacitor near pins 13 and 17. A 470nF ceramic capacitor is sufficient. |  |

| SD0                   | 14            | DO VIO                | SPI serial data output.                                                                                                                                                                                                                                                    |  |

| SDI (CFG3)            | 15            | DI VIO                | Data input of SPI interface / Microstep resolution control input in standalone mode: 0: MRES=256 microsteps; 1: MRES=16 microsteps with interpolation                                                                                                                      |  |

| SCK (CFG2)            | 16            | DI VIO                | Serial clock input of SPI interface / Chopper hysteresis control input in standalone mode: 0: HEND=4, HSTRT=2; 1: HEND=4, HSTRT=6                                                                                                                                          |  |

| GND                   | 17, 39,<br>44 |                       | Digital and analog low power GND.                                                                                                                                                                                                                                          |  |

| CSN (CFG1)            | 18            | DI VIO                | Chip select input of SPI interface / Current control input in standalone mode: 0: Current scale CS=15; 1: Current scale CS=31                                                                                                                                              |  |

| ENN                   | 19            | DI VIO                | Power MOSFET enable input. All MOSFETs are switched off when disabled. (Active low.)                                                                                                                                                                                       |  |

| CLK                   | 21            | DI VIO                | System clock input for all internal operations. Tie low to use the on-chip oscillator. A high signal disables the on-chip oscillator until power down.                                                                                                                     |  |

| VHS                   | 35            |                       | High-side supply voltage (motor supply voltage - 10V)                                                                                                                                                                                                                      |  |

| VS                    | 36            |                       | Motor supply voltage                                                                                                                                                                                                                                                       |  |

| TST_ANA /<br>ST_ALONE | 37            | AO/ DI<br>VIO<br>(pd) | non-C-Type: Leave open for normal operation. C-Type only: Tie to VCC_IO for non-SPI, stand-alone mode. Internal 10k pulldown resistor.                                                                                                                                     |  |

| SG_TST                | 38            | DO VIO                | StallGuard2 output. Signals a motor stall. (Active high.)                                                                                                                                                                                                                  |  |

| VCC_IO                | 40            |                       | Input/output supply voltage VIO for all digital pins. Tie to digital logic supply voltage. Operation is allowed in 3.3V and 5V systems.                                                                                                                                    |  |

| DIR                   | 41            | DI VIO                | Direction input. Sampled on an active edge of the STEP input to determine stepping direction. Sampling a low increases the microstep counter, while sampling a high decreases the counter. A 60-ns internal glitch filter rejects short pulses on this input.              |  |

| STEP                  | 42            | DI VIO                | Step input. Active edges can be rising or both rising and falling, as controlled by the DEDGE mode bit. A 60-ns internal glitch filter rejects short pulses on this input.                                                                                                 |  |

| TST_MODE              | 43            | DI VIO                | Test mode input. Puts IC into test mode. Tie to GND for normal operation.                                                                                                                                                                                                  |  |

| n.c.                  | 1, 33         |                       | No internal connection - can be tied to any net, e.g., in order to improve power routing to pins VSA and VSB.                                                                                                                                                              |  |

| n.c.                  | 20, 34        |                       | No internal connection                                                                                                                                                                                                                                                     |  |

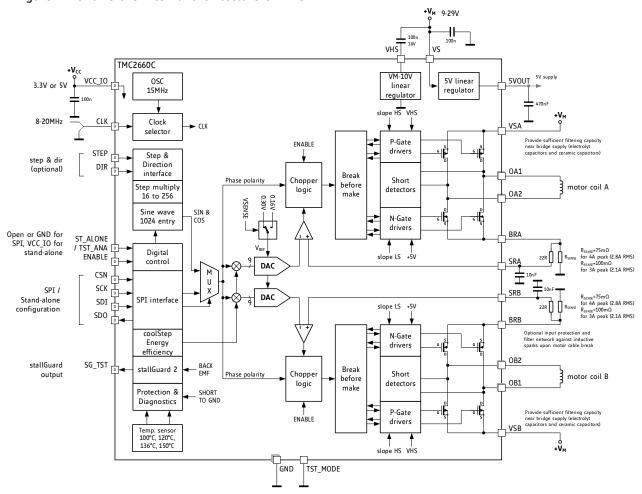

## 3 Internal Architecture

Figure 3.1 shows the internal architecture of TMC2660.

Figure 3.1 TMC2660 block diagram

#### PROMINENT FEATURES INCLUDE:

| Oscillator and clock selector      | provide the system clock from the on-chip oscillator or an external source.                                                                                                                          |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step and direction interface       | uses a microstep counter and sine table to generate target currents for the coils.                                                                                                                   |

| SPI interface                      | configures current setting, and chopper and optionally receives commands that directly set the coil current values.                                                                                  |

| Multiplexer                        | selects either the output of the sine table or the SPI interface for controlling the current into the motor coils.                                                                                   |

| Multipliers                        | scale down the currents to both coils when the currents are greater than those required by the load on the motor or as set by the CS current scale parameter.                                        |

| DACs and comparators               | convert the digital current values to analog signals that are compared with the voltages on the sense resistors. Comparator outputs terminate chopper drive phases when target currents are reached. |

| Break-before-make and gate drivers | ensure non-overlapping pulses, boost pulse voltage, and control pulse slope to the gates of the power MOSFETs.                                                                                       |

| On-chip voltage regulators         | provide high-side voltage for P-channel MOSFET gate drivers and supply voltage for on-chip analog and digital circuits.                                                                              |

## 4 Standalone Operation

Standalone operation is the easiest way to use the IC. In this mode, three pins configure for the most common settings. Just use the standard application circuit, tie low / high the SPI input pins to set the desired basic operation parameters and choose a sense resistor to fit the required motor current. However, advanced configuration and access to individual diagnostics only is possible via SPI.

| CSN: SELECTION OF MOTOR CURRENT (USE FOR STANDSTILL CURRENT REDUCTION) |                                                                               |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| CSN (CFG1)                                                             | Chopper Setting                                                               |  |  |

| GND                                                                    | Current Scale CS=15.                                                          |  |  |

|                                                                        | Use for standstill current reduction, or to adapt lower sense resistor value. |  |  |

| VCC_IO                                                                 | Current Scale CS=31.                                                          |  |  |

|                                                                        | Maximum current. Control motor current by adapting sense resistors.           |  |  |

| SCK: SELECTION OF CHOPPER HYSTERESIS (ADAPT FOR LOWEST MOTOR NOISE & VIBRATION) |                                                                              |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| SCK (CFG2) Chopper Setting                                                      |                                                                              |  |  |

| GND                                                                             | Low hysteresis (HSTRT=2, HEND=4), use for larger motor.                      |  |  |

| VCC_IO                                                                          | Medium hysteresis (HSTRT=6, HEND=4), typical for Nema17 or smaller motor, or |  |  |

|                                                                                 | for high speed motors with high coil currents.                               |  |  |

| SDI: SELECTION OF MICROSTEP RESOLUTION (ADAPT TO STEP PULSE GENERATOR) |                                                             |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| SDI (CFG3) Chopper Setting                                             |                                                             |  |  |

| GND                                                                    | 256 Microsteps full resolution for Step/Dir interface       |  |  |

| VCC_IO                                                                 | 16 Microsteps with internal interpolation to 256 microsteps |  |  |

Figure 2 Standalone configuration

Standalone mode automatically enables resonance dampening (EN\_PFD) and 136°C overtemperature detection (OT\_SENSE), sensitive high-side short detection (SHRTSENSE) and enable low side short protection (S2VS). Driver strength becomes set to SLPL=SLPH=3. TOFF is 4, TBL is 36 clocks in this mode. All other bits are cleared to 0.

In standalone configuration, StallGuard level is fixed to SGT=2. This setting will work for homing with many 42mm and larger motors in a suitable velocity range. Adapt to full or half current as fitting using CSN configuration pin.

Resulting configuration words: SDI=0: \$00200 / SDI=1: \$00204 SCK=0: \$90224 / SCK=1: \$90264 CSN=0: \$C020F / CSN=1: \$C021F

\$E810F, \$A0000

## 5 StallGuard2 Load Measurement

StallGuard2 provides an accurate measurement of the load on the motor. It can be used for stall detection as well as other uses at loads below those which stall the motor, such as CoolStep load-adaptive current reduction. (StallGuard2 is a more precise evolution of the earlier StallGuard technology.)

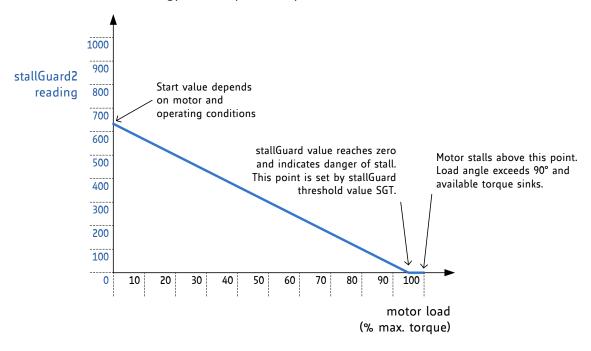

The StallGuard2 measurement value changes linearly over a wide range of load, velocity, and current settings, as shown in Figure 5.1. At maximum motor load, the value goes to zero or near to zero. This corresponds to a load angle of 90° between the magnetic field of the coils and magnets in the rotor. This also is the most energy-efficient point of operation for the motor.

Figure 5.1 StallGuard2 load measurement SG as a function of load

Two parameters control StallGuard2 and one status value is returned.

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                         | Setting | Comment            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|

| SGT       | 7-bit signed integer that sets the StallGuard2 threshold level for asserting the SG_TST output and sets the optimum measurement range for                                                                                                                                                                                                                                                           | 0       | indifferent value  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                     | +1 +63  | less sensitivity   |

|           | readout. Negative values increase sensitivity, and positive values reduce sensitivity, so more torque is required to indicate a stall. Zero is a good starting value.                                                                                                                                                                                                                               |         | higher sensitivity |

| SFILT     | Mode bit which enables the StallGuard2 filter for                                                                                                                                                                                                                                                                                                                                                   | 0       | standard mode      |

|           | more precision. If set, reduces the measurement frequency to one measurement per four fullsteps. If cleared, no filtering is performed. Filtering compensates for mechanical asymmetries in the construction of the motor, but at the expense of response time. Unfiltered operation is recommended for rapid stall detection. Filtered operation is recommended for more precise load measurement. | 1       | filtered mode      |

| Status word | Description                                      | Range  | Comment               |

|-------------|--------------------------------------------------|--------|-----------------------|

| SG          | 10-bit unsigned integer StallGuard2              | 0 1023 | 0: highest load       |

|             | measurement value. A higher value indicates      |        | low value: high load  |

|             | lower mechanical load. A lower value indicates   |        | high value: less load |

|             | a higher load and therefore a higher load angle. |        |                       |

|             | For stall detection, adjust SGT to return an SG  |        |                       |

|             | value of 0 or slightly higher upon maximum       |        |                       |

|             | motor load before stall.                         |        |                       |

## 5.1 Tuning the StallGuard2 Threshold

Due to the dependency of the StallGuard2 value SG from motor-specific characteristics and application-specific demands on load and velocity the easiest way to tune the StallGuard2 threshold SGT for a specific motor type and operating conditions is interactive tuning in the actual application.

The procedure is:

- 1. Operate the motor at a reasonable velocity for your application and monitor SG.

- 2. Apply slowly increasing mechanical load to the motor. If the motor stalls before SG reaches zero, decrease SGT. If SG reaches zero before the motor stalls, increase SGT. A good SGT starting value is zero. SGT is signed, so it can have negative or positive values.

- 3. The optimum setting is reached when SG is between 0 and 400 at increasing load shortly before the motor stalls, and SG increases by 100 or more without load. SGT in most cases can be tuned together with the motion velocity in a way that SG goes to zero when the motor stalls and the stall output SG\_TST is asserted. This indicates that a step has been lost.

The system clock frequency affects SG. An external crystal-stabilized clock should be used for applications that demand the highest precision. The power supply voltage also affects SG, so tighter regulation results in more accurate values. SG measurement has a high resolution, and there are a few ways to enhance its accuracy, as described in the following sections.

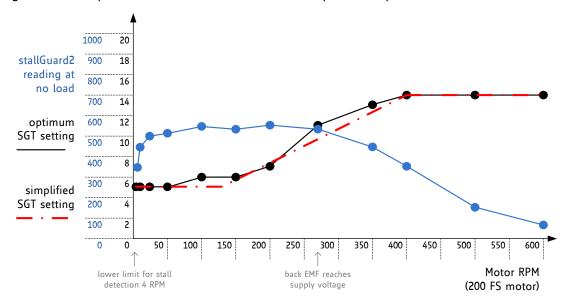

## 5.1.1 Variable Velocity Operation

Across a range of velocities, on-the-fly adjustment of the StallGuard2 threshold SGT improves the accuracy of the load measurement SG. This also improves the power reduction provided by CoolStep, which is driven by SG. Linear interpolation between two SGT values optimized at different velocities is a simple algorithm for obtaining most of the benefits of on-the-fly SGT adjustment, as shown in Figure 5.2. An optimal SGT curve in black and a two-point interpolated SGT curve in red are shown.

Figure 5.2 Linear interpolation for optimizing SGT with changes in velocity.

#### 5.1.2 Small Motors with High Torque Ripple and Resonance

Motors with a high detent torque show an increased variation of the StallGuard2 measurement value SG with varying motor currents, especially at low currents. For these motors, the current dependency might need correction in a similar manner to velocity correction for obtaining the highest accuracy.

### 5.1.3 Temperature Dependence of Motor Coil Resistance

Motors working over a wide temperature range may require temperature correction, because motor coil resistance increases with rising temperature. This can be corrected as a linear reduction of SG at increasing temperature, as motor efficiency is reduced.

### 5.1.4 Accuracy and Reproducibility of StallGuard2 Measurement

In a production environment, it may be desirable to use a fixed SGT value within an application for one motor type. Most of the unit-to-unit variation in StallGuard2 measurements results from manufacturing tolerances in motor construction. The measurement error of StallGuard2 – provided that all other parameters remain stable – can be as low as:

$stallGuard\ measurement\ error = \pm max(1, |SGT|)$

## 5.2 StallGuard2 Measurement Frequency and Filtering

The StallGuard2 measurement value SG is updated with each full step of the motor. This is enough to safely detect a stall, because a stall always means the loss of four full steps. In a practical application, especially when using CoolStep, a more precise measurement might be more important than an update for each fullstep because the mechanical load never changes instantaneously from one step to the next. For these applications, the SFILT bit enables a filtering function over four load measurements. The filter should always be enabled when high-precision measurement is required. It compensates for variations in motor construction, for example due to misalignment of the phase A to phase B magnets. The filter should only be disabled when rapid response to increasing load is required, such as for stall detection at high velocity.

## 5.3 Detecting a Motor Stall

To safely detect a motor stall, a stall threshold must be determined using a specific SGT setting. Therefore, you need to determine the maximum load the motor can drive without stalling and to monitor the SG value at this load, for example some value within the range 0 to 400. The stall threshold should be a value safely within the operating limits, to allow for parameter stray. So, your microcontroller software should set a stall threshold which is slightly higher than the minimum value seen before an actual motor stall occurs. The response at an SGT setting at or near 0 gives some idea on the quality of the signal: Check the SG value without load and with maximum load. These values should show a difference of at least 100 or a few 100, which shall be large compared to the offset. If you set the SGT value so that a reading of 0 occurs at maximum motor load, an active high stall output signal will be available at SG\_TST output.

## 5.4 Limits of StallGuard2 Operation

StallGuard2 does not operate reliably at extreme motor velocities: Very low motor velocities (for many motors, less than one revolution per second) generate a low back EMF and make the measurement unstable and dependent on environment conditions (temperature, etc.). Other conditions will also lead to extreme settings of SGT and poor response of the measurement value SG to the motor load.

Very high motor velocities, in which the full sinusoidal current is not driven into the motor coils also lead to poor response. These velocities are typically characterized by the motor back EMF reaching the supply voltage.

# 6 CoolStep Load-Adaptive Current Control

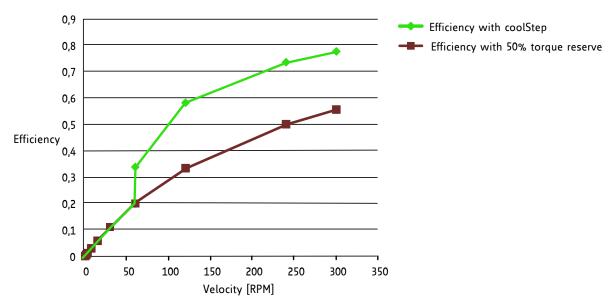

CoolStep allows substantial energy savings, especially for motors which see varying loads or operate at a high duty cycle. Because a stepper motor application needs to work with a torque reserve of 30% to 50%, even a constant-load application allows significant energy savings because CoolStep automatically enables torque reserve when required. Reducing power consumption keeps the system cooler, increases motor life, and allows reducing cost in the power supply and cooling components.

Hint

Reducing motor current by half results in reducing power by a factor of four.

Energy efficiency - power consumption decreased up to 75%.

Motor generates less heat - improved mechanical precision.

Less cooling infrastructure - for motor and driver.

Cheaper motor - does the job.

Figure 6.1 Energy efficiency example with CoolStep

Figure 6.1 shows the efficiency gain of a 42mm stepper motor when using CoolStep compared to standard operation with 50% of torque reserve. CoolStep is enabled above 60rpm in the example.

CoolStep is controlled by several parameters, but two are critical for understanding how it works:

| Parameter | Description                                                                                                                                                                                                                                                                                                                            | Range | Comment                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------|

| SEMIN     | 4-bit unsigned integer that sets a lower threshold. If SG goes below this threshold, CoolStep increases the current to both coils. The 4-bit SEMIN value is scaled by 32 to cover the lower half of the range of the 10-bit SG value. (The name of this parameter is derived from smartEnergy, which is an earlier name for CoolStep.) |       | lower CoolStep<br>threshold:<br>SEMINx32           |

| SEMAX     | 4-bit unsigned integer that controls an upper threshold. If SG is sampled equal to or above this threshold enough times, CoolStep decreases the current to both coils. The upper threshold is (SEMIN + SEMAX + 1) x 32.                                                                                                                |       | upper CoolStep<br>threshold:<br>(SEMIN+SEMAX+1)x32 |

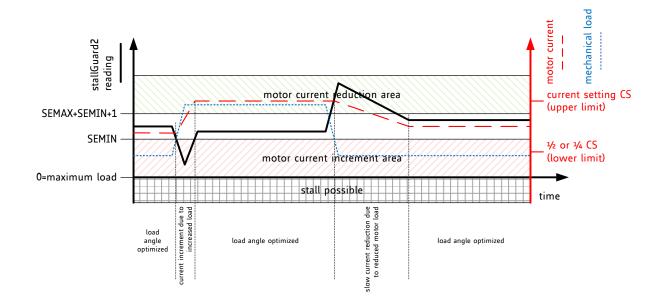

Figure 6.2 shows the operating regions of CoolStep. The black line represents the SG measurement value, the blue line represents the mechanical load applied to the motor, and the red line represents

the current into the motor coils. When the load increases, SG falls below SEMIN, and CoolStep increases the current. When the load decreases and SG rises above (SEMIN + SEMAX + 1)  $\times$  32 the current becomes reduced.

Figure 6.2 CoolStep adapts motor current to the load.

Four more parameters control CoolStep and one status value is returned:

| Parameter   | Description                                                                                                                                                                                                                                                                                                                                                                                                | Range | Comment                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------|

| CS          | Current scale. Scales both coil current values as taken from the internal sine wave table or from the SPI interface. For high precision motor operation, work with a current scaling factor in the range 16 to 31, because scaling down the current values reduces the effective microstep resolution by making microsteps coarser. This setting also controls the maximum current value set by CoolStep™. | O 31  | scaling factor:<br>1/32, 2/32, 32/32                                            |

| SEUP        | Number of increments of the coil current for each occurrence of an SG measurement below the lower threshold.                                                                                                                                                                                                                                                                                               | 0 3   | step width is:<br>1, 2, 4, 8                                                    |

| SEDN        | Number of occurrences of SG measurements above the upper threshold before the coil current is decremented.                                                                                                                                                                                                                                                                                                 | 0 3   | number of StallGuard<br>measurements per<br>decrement: 32, 8, 2, 1              |

| SEIMIN      | Mode bit that controls the lower limit for scaling the coil current. If the bit is set, the limit is 1/4 CS. If the bit is clear, the limit is 1/2 CS.                                                                                                                                                                                                                                                     |       | Minimum motor<br>current:<br>1/2 of CS<br>1/4 of CS                             |

| Status word | Description                                                                                                                                                                                                                                                                                                                                                                                                | Range | Comment                                                                         |

| SE          | 5-bit unsigned integer reporting the actual current scaling value determined by CoolStep. This value is biased by 1 and divided by 32, so the range is 1/32 to 32/32. The value will not be greater than the value of CS or lower than either 1/4 CS or 1/2 CS depending on SEIMIN setting.                                                                                                                |       | Actual motor current<br>scaling factor set by<br>CoolStep:<br>1/32, 2/32, 32/32 |

## 6.1 Tuning CoolStep

Before tuning CoolStep, first tune the StallGuard2 threshold level SGT, which affects the range of the load measurement value SG. CoolStep uses SG to operate the motor near the optimum load angle of +90°.

The current increment speed is specified in SEUP, and the current decrement speed is specified in SEDN. They can be tuned separately because they are triggered by different events that may need different responses. The encodings for these parameters allow the coil currents to be increased much more quickly than decreased, because crossing the lower threshold is a more serious event that may require a faster response. If the response is too slow, the motor may stall. In contrast, a slow response to crossing the upper threshold does not risk anything more serious than missing an opportunity to save power.

Hint

CoolStep operates between limits controlled by the current scale parameter CS and the SEIMIN bit.

#### 6.1.1 Response Time

For fast response to increasing motor load, use a high current increment step SEUP. If the motor load changes slowly, a lower current increment step can be used to avoid motor current oscillations. If the filter controlled by SFILT is enabled, the measurement rate and regulation speed are cut by a factor of four.

### 6.1.2 Low Velocity and Standby Operation

Because StallGuard2 is not able to measure the motor load in standstill and at very low RPM, the current at low velocities should be set to an application-specific default value and combined with standstill current reduction settings programmed through the SPI interface.

### 7 SPI Interface

The TMC2660 allows full control over all configuration parameters and mode bits through the SPI interface. An initialization is required prior to motor operation. The SPI interface also allows reading back status values and bits.

## 7.1 Bus Signals

The SPI bus on the TMC2660 has four signals:

SCK bus clock input SDI serial data input SDO serial data output

CSN chip select input (active low)

The slave is enabled for an SPI transaction by a low on the chip select input CSN. Bit transfer is synchronous to the bus clock SCK, with the slave latching the data from SDI on the rising edge of SCK and driving data to SDO following the falling edge. The most significant bit is sent first. A minimum of 20 SCK clock cycles is required for a bus transaction with the TMC2660.

If more than 20 clocks are driven, the additional bits shifted into SDI are shifted out on SDO after a 20-clock delay through an internal shift register. This can be used for daisy chaining multiple chips.

CSN must be low during the whole bus transaction. When CSN goes high, the contents of the internal shift register are latched into the internal control register and recognized as a command from the master to the slave. If more than 20 bits are sent, only the last 20 bits received before the rising edge of CSN are recognized as the command.

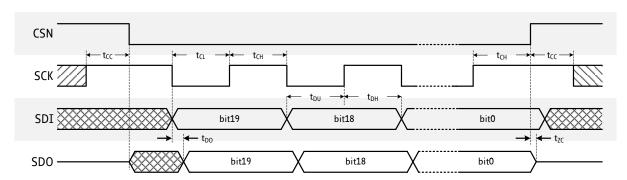

## 7.2 Bus Timing

SPI interface is synchronized to the internal system clock, which limits the SPI bus clock SCK to half of the system clock frequency. If the system clock is based on the on-chip oscillator, an additional 10% safety margin must be used to ensure reliable data transmission. All SPI inputs as well as the ENN input are internally filtered to avoid triggering on pulses shorter than 20ns. Figure 7.1 shows the timing parameters of an SPI bus transaction, and the table below specifies their values.

Figure 7.1 SPI Timing

#### Hint

Usually this SPI timing is referred to as SPI MODE 3. Data change is at the negative SCK edge, and SCK return to high level. CSN spans the complete 20 Bit transmission.

| SPI Interface Timing                             | AC-Characteristics clock period is t <sub>CLK</sub> |                                                                                         |                  |                           |                      |      |  |  |

|--------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|---------------------------|----------------------|------|--|--|

| Parameter                                        | Symbol                                              | Conditions                                                                              | Min              | Тур                       | Max                  | Unit |  |  |

| SCK valid before or after change of CSN          | t <sub>cc</sub>                                     |                                                                                         | 10               |                           |                      | ns   |  |  |

| CSN high time                                    | t <sub>сsн</sub>                                    | *Min time is for synchronous CLK with SCK high one $t_{\text{CH}}$ before CSN high only | t <sub>CLK</sub> | >2t <sub>CLK</sub><br>+10 |                      | ns   |  |  |

| SCK low time                                     | t <sub>CL</sub>                                     | *)Min time is for<br>synchronous CLK<br>only                                            | t <sub>CLK</sub> | >t <sub>CLK</sub> +10     |                      | ns   |  |  |

| SCK high time                                    | t <sub>CH</sub>                                     | *)Min time is for<br>synchronous CLK<br>only                                            | t <sub>CLK</sub> | >t <sub>CLK</sub> +10     |                      | ns   |  |  |

| SCK frequency using internal clock               | f <sub>SCK</sub>                                    | Assumes minimum OSC frequency                                                           |                  |                           | 4                    | MHz  |  |  |

| SCK frequency using external 16MHz clock         | f <sub>SCK</sub>                                    | Assumes synchronous CLK                                                                 |                  |                           | 8                    | MHz  |  |  |

| SDI setup time before rising edge of SCK         | t <sub>DU</sub>                                     |                                                                                         | 10               |                           |                      | ns   |  |  |

| SDI hold time after rising edge of SCK           | t <sub>DH</sub>                                     |                                                                                         | 10               |                           |                      | ns   |  |  |

| Data out valid time after falling SCK clock edge | t <sub>DO</sub>                                     | No capacitive load on SDO                                                               |                  |                           | t <sub>FILT</sub> +5 | ns   |  |  |

| SDI, SCK, and CSN filter delay time              | t <sub>FILT</sub>                                   | Rising and falling edge                                                                 | 12               | 20                        | 30                   | ns   |  |  |

### 7.3 Bus Architecture

SPI slaves can be chained and used with a single chip select line. If slaves are chained, they behave like a long shift register. For example, a chain of two motor drivers requires 40 bits to be sent. The last bits shifted to each register in the chain are loaded into an internal register on the rising edge of the CSN input. For example, 24 or 32 bits can be sent to a single motor driver, but it latches just the last 20 bits received before CSN goes high.

Figure 7.2 Interfaces to a TMC429 motion controller chip and a TMC2660 motor driver

Figure 7.2 shows the interfaces in a typical application. The SPI bus is used by an embedded MCU to initialize the control registers of both a motion controller and one or more motor drivers. STEP/DIR interfaces are used between the motion controller and the motor drivers.

# 7.4 Register Write Commands

An SPI bus transaction to the TMC2660 is a write command to one of the five write-only registers that hold configuration parameters and mode bits:

| Register                                      | Description                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Driver Control Register<br>(DRVCTRL)          | The DRVCTRL register has different formats for controlling the interface to the motion controller depending on whether or not the STEP/DIR interface is enabled.                                                                                                                          |

| Chopper Configuration Register (CHOPCONF)     | The CHOPCONF register holds chopper parameters and mode bits.                                                                                                                                                                                                                             |

| CoolStep Configuration Register (SMARTEN)     | The SMARTEN register holds CoolStep parameters and a mode bit. (smartEnergy is an earlier name for CoolStep.)                                                                                                                                                                             |

| StallGuard2 Configuration Register (SGCSCONF) | The SGCSCONF register holds StallGuard2 parameters and a mode bit.                                                                                                                                                                                                                        |

| Driver Configuration Register<br>(DRVCONF)    | The DRVCONF register holds parameters and mode bits used to control the power MOSFETs and the protection circuitry. It also holds the SDOFF bit which controls the STEP/DIR interface and the RDSEL parameter which controls the contents of the response returned in an SPI transaction. |

In the following sections, multibit binary values are prefixed with a % sign, for example %0111.

#### 7.4.1 Write Command Overview

The table below shows the formats for the five register write commands. Bits 19, 18, and sometimes 17 select the register being written, as shown in bold. The DRVCTRL register has two formats, as selected by the SDOFF bit. Bits shown as 0 must always be written as 0, and bits shown as 1 must always be written with 1. Detailed descriptions of each parameter and mode bit are given in the following sections.

| Register/ | DRVCTRL   | DRVCTRL   | CHOPCONF | SMARTEN | SGCSCONF | DRVCONF     |

|-----------|-----------|-----------|----------|---------|----------|-------------|

| Bit       | (SDOFF=1) | (SDOFF=0) |          |         |          |             |

| 19        | 0         | 0         | 1        | 1       | 1        | 1           |

| 18        | 0         | 0         | 0        | 0       | 1        | 1           |

| 17        | PHA       | 0         | 0        | 1       | 0        | 1           |

| 16        | CA7       | 0         | TBL1     | 0       | SFILT    | TST         |

| 15        | CA6       | 0         | TBL0     | SEIMIN  | 0        | SLPH1       |

| 14        | CA5       | 0         | CHM      | SEDN1   | SGT6     | SLPH0       |

| 13        | CA4       | 0         | RNDTF    | SEDN0   | SGT5     | SLPL1       |

| 12        | CA3       | 0         | HDEC1    | 0       | SGT4     | SLPL0       |

| 11        | CA2       | 0         | HDEC0    | SEMAX3  | SGT3     | 0           |

| 10        | CA1       | 0         | HEND3    | SEMAX2  | SGT2     | DISS2G      |

| 9         | CA0       | INTPOL    | HEND2    | SEMAX1  | SGT1     | TS2G1       |

| 8         | PHB       | DEDGE     | HEND1    | SEMAX0  | SGT0     | TS2G0       |

| 7         | CB7       | 0         | HEND0    | 0       | 0        | SDOFF       |

| 6         | CB6       | 0         | HSTRT2   | SEUP1   | 0        | VSENSE      |

| 5         | CB5       | 0         | HSTRT1   | SEUP0   | 0        | RDSEL1      |

| 4         | CB4       | 0         | HSTRT0   | 0       | CS4      | RDSEL0      |

| 3         | CB3       | MRES3     | TOFF3    | SEMIN3  | CS3      | OTSENS *)   |

| 2         | CB2       | MRES2     | TOFF2    | SEMIN2  | CS2      | SHRTSENS *) |

| 1         | CB1       | MRES1     | TOFF1    | SEMIN1  | CS1      | EN_PFD *)   |

| 0         | CB0       | MRES0     | TOFF0    | SEMIN0  | CS0      | EN_S2VS *)  |

<sup>\*)</sup> Additional option for TMC2660C only. Setting these bits for TMC2660 does not have any effect.

## 7.4.2 Read Response Overview

The table below shows the formats for the read response. The RDSEL parameter in the DRVCONF register selects the format of the read response.

| Bit | RDSEL=%00                    | RDSEL=%01                    | RDSEL=%10 | RDSEL=%11*) |  |  |

|-----|------------------------------|------------------------------|-----------|-------------|--|--|

| 19  | MSTEP9                       | SG9                          | SG9       | UV_7V       |  |  |

| 18  | MSTEP8                       | SG8                          | SG8       | ENN input   |  |  |

| 17  | MSTEP7                       | SG7                          | SG7       | S2VSB       |  |  |

| 16  | MSTEP6                       | SG6                          | SG6       | S2GB        |  |  |

| 15  | MSTEP5                       | SG5                          | SG5       | S2VSA       |  |  |

| 14  | MSTEP4                       | SG4                          | SE4       | S2GA        |  |  |

| 13  | MSTEP3                       | SG3                          | SE3       | OT150       |  |  |

| 12  | MSTEP2                       | SG2                          | SE2       | OT136       |  |  |

| 11  | MSTEP1                       | SG1                          | SE1       | OT120       |  |  |

| 10  | MSTEP0                       | SG0                          | SE0       | OT100       |  |  |

| 9   | 0                            | 0                            | 0         | 1           |  |  |

| 8   | 0                            | 0                            | 0         | 1           |  |  |

| 7   | STST                         |                              |           |             |  |  |

| 6   | OLB                          |                              |           |             |  |  |

| 5   | OLA                          |                              |           |             |  |  |

| 4   | SHORTB (S2GE                 | SHORTB (S2GB for non-C-type) |           |             |  |  |

| 3   | SHORTA (S2GA for non-C-type) |                              |           |             |  |  |

| 2   | OTPW                         |                              |           |             |  |  |

| 1   | OT                           |                              |           |             |  |  |

| 0   | SG                           |                              |           | _           |  |  |

# 7.5 Driver Control Register (DRVCTRL)

The format of the DRVCTRL register depends on the state of the SDOFF mode bit.

SPI Mode SDOFF bit is set, the STEP/DIR interface is disabled, and DRVCTRL is the interface for

specifying the currents through each coil.

STEP/DIR Mode SDOFF bit is clear, the STEP/DIR interface is enabled, and DRVCTRL is a configuration

register for the STEP/DIR interface.

# 7.5.1 DRVCTRL Register in SPI Mode

| DRVCTRL Driver Cont |      | Driver Control in SPI M | ode (SDOFF=1)                                               |

|---------------------|------|-------------------------|-------------------------------------------------------------|

| Bit                 | Name | Function                | Comment                                                     |

| 19                  | 0    | Register address bit    |                                                             |

| 18                  | 0    | Register address bit    |                                                             |

| 17                  | PHA  | Polarity A              | Sign of current flow through coil A:                        |

|                     |      |                         | 0: Current flows from OA1 pins to OA2 pins.                 |

|                     |      |                         | 1: Current flows from OA2 pins to OA1 pins.                 |

| 16                  | CA7  | Current A MSB           | Magnitude of current flow through coil A. The range is      |

| 15                  | CA6  |                         | 0 to 248, if hysteresis or offset are used up to their full |

| 14                  | CA5  |                         | extent. The resulting value after applying hysteresis or    |

| 13                  | CA4  |                         | offset must not exceed 255.                                 |

| 12                  | CA3  |                         |                                                             |

| 11                  | CA2  |                         |                                                             |

| 10                  | CA1  |                         |                                                             |

| 9                   | CA0  | Current A LSB           |                                                             |

| 8                   | PHB  | Polarity B              | Sign of current flow through coil B:                        |

|                     |      |                         | 0: Current flows from OB1 pins to OB2 pins.                 |

|                     |      |                         | 1: Current flows from OB2 pins to OB1 pins.                 |

| 7                   | CB7  | Current B MSB           | Magnitude of current flow through coil B. The range is      |

| 6                   | CB6  |                         | 0 to 248, if hysteresis or offset are used up to their full |

| 5                   | CB5  |                         | extent. The resulting value after applying hysteresis or    |

| 4                   | CB4  |                         | offset must not exceed 255.                                 |

| 3                   | CB3  |                         |                                                             |

| 2                   | CB2  |                         |                                                             |

| 1                   | CB1  |                         |                                                             |

| 0                   | CB0  | Current B LSB           |                                                             |

# 7.5.2 DRVCTRL Register in STEP/DIR Mode

| DRVC | DRVCTRL Driver Control in STEP/I |                      | DIR Mode (SDOFF=0)                                      |

|------|----------------------------------|----------------------|---------------------------------------------------------|

| Bit  | Name                             | Function             | Comment                                                 |

| 19   | 0                                | Register address bit |                                                         |

| 18   | 0                                | Register address bit |                                                         |

| 17   | 0                                | Reserved             |                                                         |

| 16   | 0                                | Reserved             |                                                         |

| 15   | 0                                | Reserved             |                                                         |

| 14   | 0                                | Reserved             |                                                         |

| 13   | 0                                | Reserved             |                                                         |

| 12   | 0                                | Reserved             |                                                         |

| 11   | 0                                | Reserved             |                                                         |

| 10   | 0                                | Reserved             |                                                         |

| 9    | INTPOL                           | Enable STEP          | 0: Disable STEP pulse interpolation.                    |

|      |                                  | interpolation        | 1: Enable STEP pulse multiplication by 16.              |

| 8    | DEDGE                            | Enable double edge   | 0: Rising STEP pulse edge is active, falling edge is    |

|      |                                  | STEP pulses          | inactive.                                               |

|      |                                  |                      | 1: Both rising and falling STEP pulse edges are active. |

| 7    | 0                                | Reserved             |                                                         |

| 6    | 0                                | Reserved             |                                                         |

| 5    | 0                                | Reserved             |                                                         |

| 4    | 0                                | Reserved             |                                                         |

| 3    | MRES3                            | Microstep resolution | Microsteps per 90°:                                     |

| 2    | MRES2                            | for STEP/DIR mode    | %0000: 256                                              |

| 1    | MRES1                            |                      | %0001: 128                                              |

| 0    | MRES0                            |                      | %0010: 64                                               |

|      |                                  |                      | %0011: 32                                               |

|      |                                  |                      | %0100: 16                                               |

|      |                                  |                      | %0101: 8                                                |

|      |                                  |                      | %0110: 4                                                |

|      |                                  |                      | %0111: 2 (halfstep)                                     |

|      |                                  |                      | %1000: 1 (fullstep)                                     |

# 7.6 Chopper Control Register (CHOPCONF)

| CHO | PCONF          | Chopper Configuration  |                    |                                                                                         |

|-----|----------------|------------------------|--------------------|-----------------------------------------------------------------------------------------|

| Bit | Name           | Function               | Commer             | it                                                                                      |

| 19  | 1              | Register address bit   |                    |                                                                                         |

| 18  | 0              | Register address bit   |                    |                                                                                         |

| 17  | 0              | Register address bit   |                    |                                                                                         |

| 16  | TBL1           | Blanking time          | _                  | time interval, in system clock periods:                                                 |

| 15  | TBL0           |                        | %00: 16            |                                                                                         |

|     |                |                        | %01: 24            |                                                                                         |

|     |                |                        | %10: 36<br>%11: 54 |                                                                                         |

| 14  | СНМ            | Chopper mode           | This mod           | de bit affects the interpretation of the HDEC, and HSTRT parameters shown below.        |

|     |                |                        | 0                  | Standard mode (SpreadCycle)                                                             |